# AUSTRALIAN RAIL TRACK CORPORATION LTD

Discipline: Engineering (Signalling)

# Design of Microlok II Interlockings

# **SCP 23**

Applicability

New South Wales ✓ CRIA (NSW CRN) ✓

**Primary Source**

| RIC Standard: SC 05 43 00 00 SP Version 1.1 |

|---------------------------------------------|

|---------------------------------------------|

# **Document Status**

| Version | Date Reviewed | Prepared by | Reviewed by          | Endorsed                        | Approved |

|---------|---------------|-------------|----------------------|---------------------------------|----------|

| 1.4     | 25 June 2010  | Standards   | Manager<br>Standards | Exec Manager<br>SS&P 25/06/2010 | CEO      |

# **Amendment Record**

| Version | Date Reviewed   | Clause                                  | Description of Amendment                                                                   |

|---------|-----------------|-----------------------------------------|--------------------------------------------------------------------------------------------|

| 1.1     | 1 October 2004  |                                         | Reformatted to ARTC Standard                                                               |

| 1.2     | 14 March 2005   | Disclaimer                              | Minor editorial change and document reformatted                                            |

| 1.3     | 13 October 2006 | General ,<br>3, 4,<br>Appendix<br>A & B | Updated to reflect amendments made by RailCorp to SC05430000SP version 1.2 dated 6 Jun 06. |

| 1.4     | 25 June 2010    |                                         | Transferred Sections 1, 2.1 and 2.2 to ESD-05-12.                                          |

© Australian Rail Track Corporation Limited 2010

Disclaimer:

This document has been prepared by ARTC for internal use and may not be relied on by any other party without ARTC's prior written consent. Use of this document shall be subject to the terms of the relevant contract with ARTC.

ARTC and its employees shall have no liability to unauthorised users of the information for any loss, damage, cost or expense incurred or arising by reason of an unauthorised user using or relying upon the information in this document, whether caused by error, negligence, omission or misrepresentation in this document.

#### This document is uncontrolled when printed.

Authorised users of this document should visit ARTC's intranet or extranet (www.artc.com.au) to access the latest version of this document.

# Contents

| 1. | Reference Documents                                  | . 3 |

|----|------------------------------------------------------|-----|

| 2. | System Configuration                                 | . 3 |

|    | 2.1. General                                         | . 3 |

|    | 2.2. Design goals                                    | . 3 |

|    | 2.3. Power supply configuration                      | . 3 |

|    | 2.4. Interlocking equipment configuration            | . 4 |

|    | 2.5. Control system communication link configuration | . 5 |

|    | 2.6. Safety system communication link configuration  | . 6 |

|    | 2.7. Equipment housing and cable route configuration | . 7 |

|    | 2.8. Microlok specific configuration issues          | . 8 |

|    | 2.9. Microlok Platform Safety Application Guidelines | 10  |

|    | 2.10. Track side equipment configuration             | 11  |

|    | 2.11. Cables and wiring                              | 14  |

| 3. | Serial Link Communications                           | 17  |

|    | 3.1. Vital Serial Links                              | 17  |

|    | 3.2. Genisys links (Control system link)             | 20  |

|    | 3.3. Control line states                             | 23  |

| 4. | Application Logic Design                             | 25  |

|    | 4.1. Introduction                                    | 25  |

|    | 4.2. Design Process                                  | 25  |

|    | 4.3. System Limitations                              | 25  |

|    | 4.4. Standardisation of OCS Control of Interlockings | 26  |

|    | 4.5. General Guidelines                              | 28  |

| 5. | Circuit Design                                       | 40  |

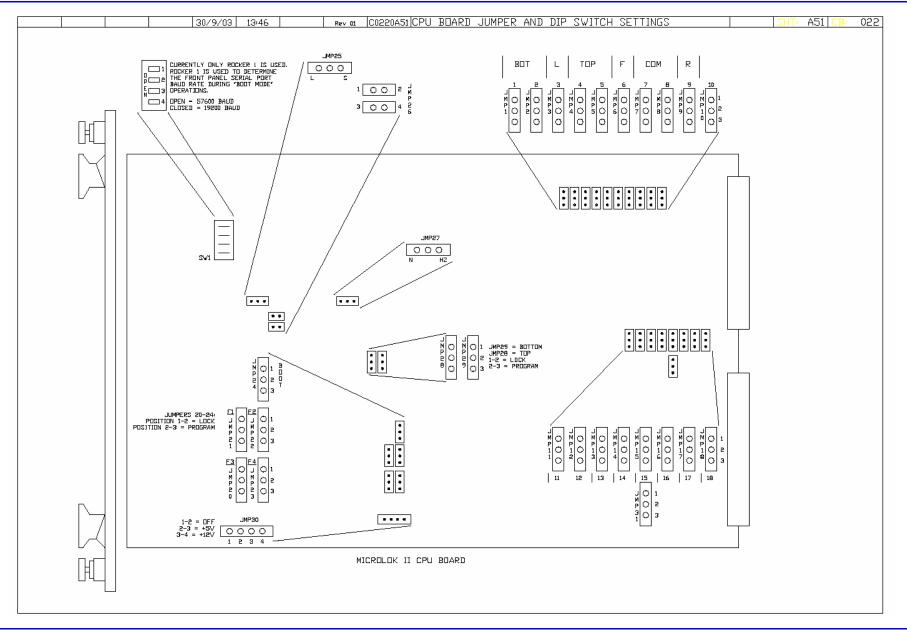

|    | 5.1. Microlok II Design Configuration and Settings   | 40  |

| 6. | Setting to Work                                      | 12  |

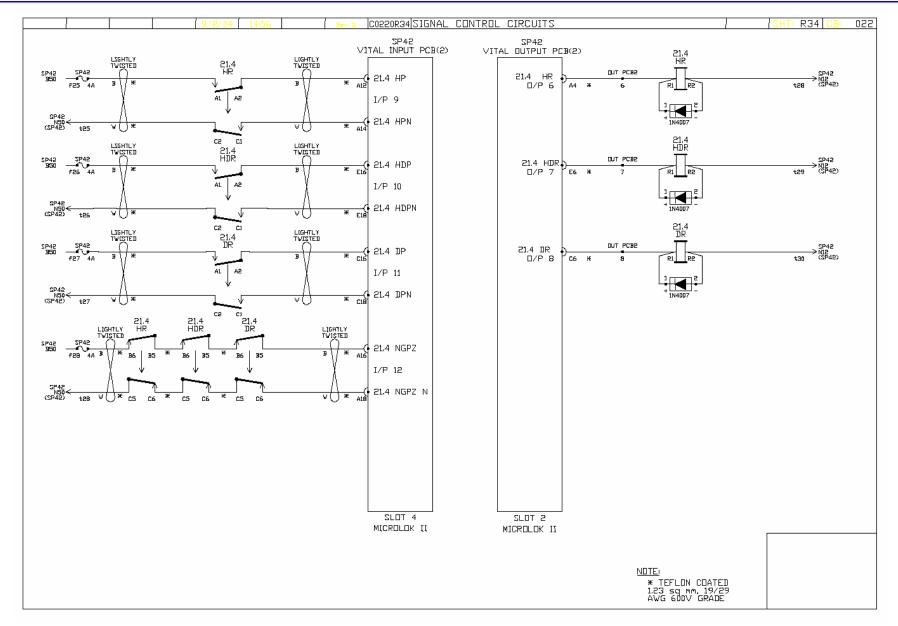

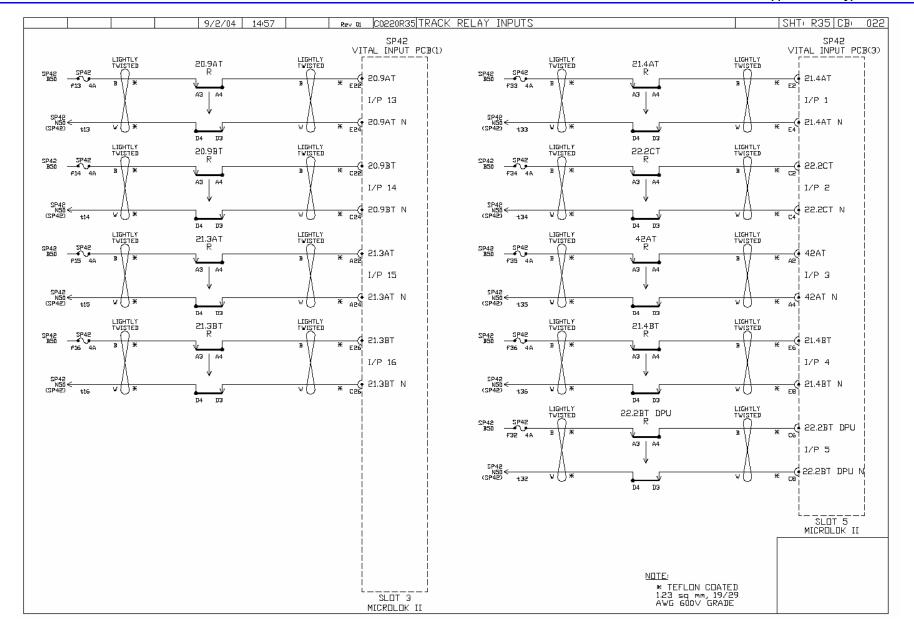

| 7. | Appendix A – Typical Circuits                        | 14  |

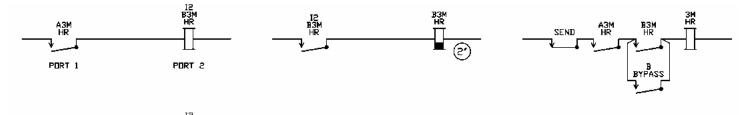

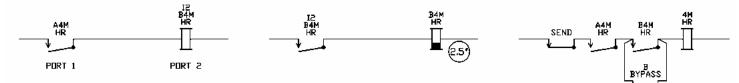

| 8. | Appendix B – Hot Standby Arrangements                | 59  |

# 1. Reference Documents

Refer to ESD-05-12 Microlok II Design.

# 2. System Configuration

# 2.1. General

Refer to ESD-05-12 Microlok II Design.

# 2.2. Design goals

Refer to ESD-05-12 Microlok II Design.

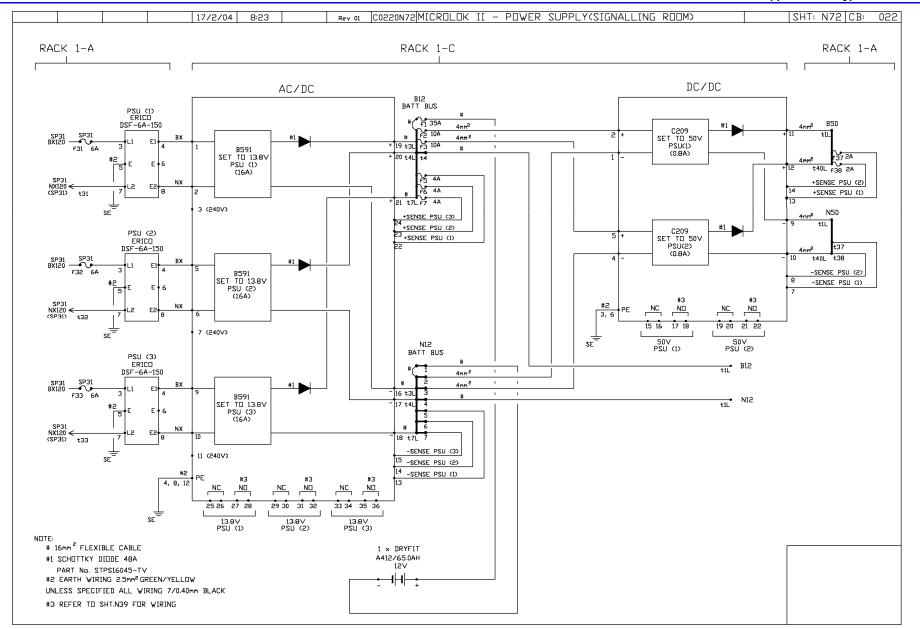

# 2.3. Power supply configuration

#### 2.3.1 General

Power load calculations are to be as per Signal Design quality procedure QSDP 48 Signals Power Design.

# 2.3.2 High traffic areas

Provide redundant supplies, and design to provide breaks of less than 10mS, with a standalone power supply capacity of 10 minutes or more. Components that are likely to fail within the life of the installation are to have redundant facilities as part of the design.

Normal and emergency supplies must be provided independently from the electricity grid.

Full galvanic isolation is required between each signalling location.

Power distribution should be at extended voltage (that is, higher than 120V).

The power system must detect "brown outs" in the normal supply and then use the other supply.

N+1 redundancy is required for all DC supplies other than track circuits which may use non-redundant DC supplies as per normal practice.

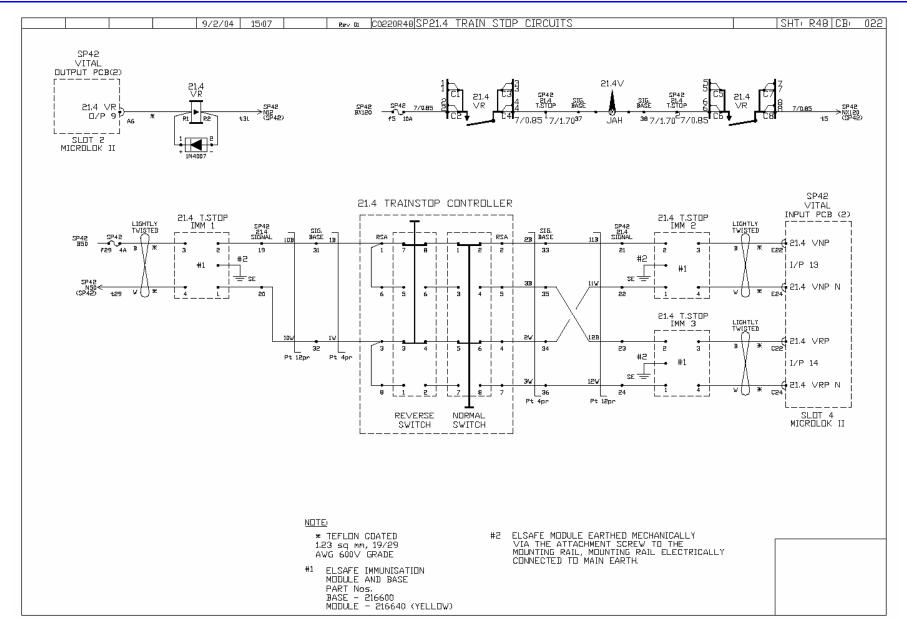

DC power supplies are to be filtered and regulated. However existing unfiltered, un-regulated DC power supplies may be used for external inputs provided that Elsafe immunisation modules (216640) are fitted at the Microlok II inputs.

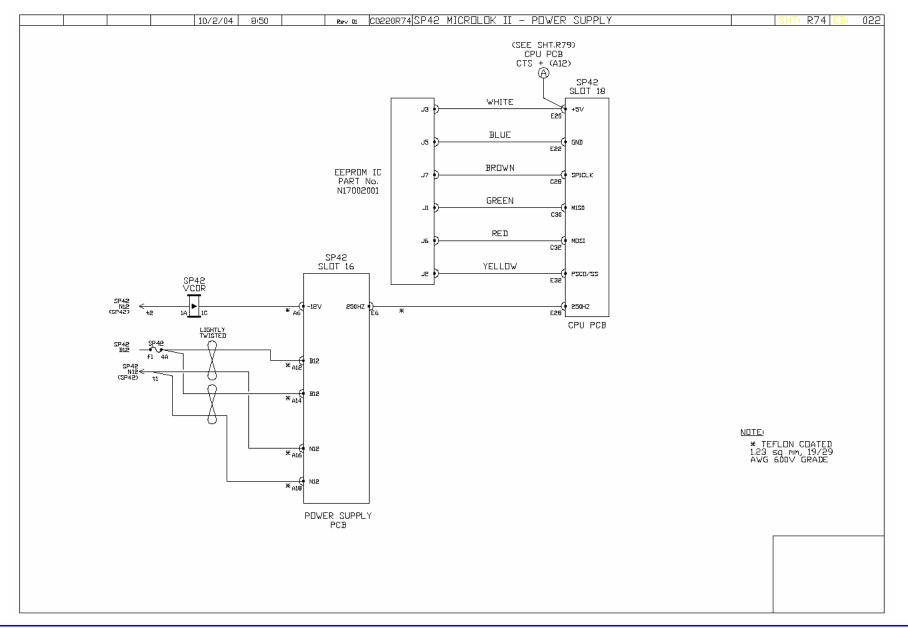

The Microlok II 12V supply is to be battery backed up as per the Microlok II manuals.

# 2.3.3 General traffic areas

Supply breaks of up to 30 seconds can be tolerated but should normally be less than 0.1 seconds and occur less than once per 3 month period.

A standalone power supply capacity of 1 minute or more must be provided.

Normal and emergency supplies must be provided from independent sources. The Normal supply must be provided from the electricity grid and a railway supply is preferred.

The emergency supply should usually be provided from the electricity grid. The emergency supply may alternatively be automatically provided by generator, or battery with a 12 hour endurance minimum.

The power system must detect "brown outs" in the normal supply and then use the other supply.

System Configuration

N+1 redundancy is required for all DC supplies other than track circuits, which may use non-redundant supplies as per normal practice for DC supplies that will cause an immediate failure.

Choose approved DC power supplies with a Mean Time Between Failures (MTBF) of greater than 100,000 hours for those DC supplies that do not have redundancy.

DC power supplies are to be filtered and regulated. However existing unfiltered, un-regulated DC power supplies may be used for external inputs provided that Elsafe immunisation modules (216640) are fitted at the Microlok II inputs.

The Microlok II 12V supply is to be battery backed up as per the Microlok II manuals.

#### 2.3.4 Low traffic areas

Supply breaks of up to 60 seconds can be tolerated but should normally be less than 10 seconds and occur less than once per month.

Normal supply can be from electricity grid or solar power. Solar power designs must have a minimum of 7 days autonomy.

Outside the electrified area the emergency supply may be provided by a motor generator, or battery with an 8 hour endurance minimum.

In some cases, not all equipment may be provided with emergency supply (eg point machines), however interlocking equipment must remain functional when operating from the emergency supply.

The power system must detect "brown outs" in the normal supply and then use the other supply.

No redundancy is required for DC supplies. Choose approved power supplies with an MTBF of greater than 100,000 hours.

DC power supplies are to be filtered and regulated. However existing unfiltered, un-regulated DC power supplies may be used for external inputs provided that Elsafe immunisation modules (216640) are fitted at the Microlok II inputs.

The Microlok II 12V supply is to be battery backed up as per the Microlok II manuals.

# 2.4. Interlocking equipment configuration

#### 2.4.1 High traffic areas

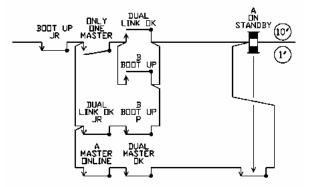

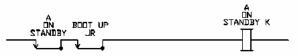

Fully redundant interlocking equipment with non–duplicated external circuits in a hot standby configuration is required.

Inputs from external equipment are commoned and wired to both Interlockings and OR'd together in the interlocking data.

Outputs are OR'd together via facilities to prevent the failure of one system affecting the loads (ie stop "back feeds").

Disconnection facilities must be provided for testing of new works and alterations without any impact on the operation of the railway.

Direct drive to LED signal lights is currently not permitted as this has the potential to cause the common mode failure of the interlocking equipment.

Individual interlockings may be split vertically if required due to processing constraints. The upper Microlok will process the inputs and interlocking controls to the system, and the lower will process the outputs and comparisons for synchronisation.

#### 2.4.2 General traffic areas

Main interlocking equipment is duplicated in a hot standby configuration.

Interlocking equipment used to interface to track-side equipment does not need to be duplicated.

Direct drive to LED signal lights is not normally permitted as this can cause the failure of the interlocking equipment due to failures of the LED module, however would be permitted where such failures can be shown to be of an impact that fails not more than 2 signals on each track.

Individual interlockings may be split vertically if required due to processing constraints. The upper Microlok will process the inputs and interlocking controls to the system, and the lower will process the outputs and comparisons for synchronisation.

#### 2.4.3 Low traffic areas

The interlocking equipment does not require redundancy for availability.

Direct drive of LED signal lights is permitted. The interlocking design must provide a method to permit disconnection as per the *Microlok Computer Based Interlocking* Signalling Maintenance Procedure SMP 38.

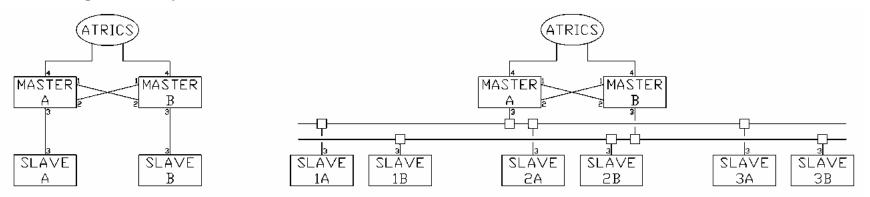

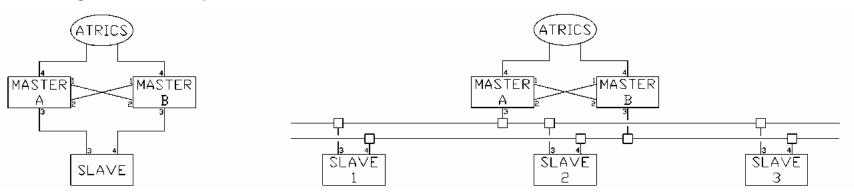

### 2.4.4 Connection to adjacent interlockings

The preferred connection to an adjacent Microlok interlocking is via vital serial links, making a slave Microlok II location as a slave of both interlocking masters.

The non-preferred connection to an adjacent Microlok interlocking is via vital serial links from Slave Microloks at adjacent locations.

The interface between a Microlok II interlocking and another type of interlocking is via relay style interface circuits.

# 2.5. Control system communication link configuration

#### 2.5.1 General

Received data may need to be conditioned by the link status as the bit states are maintained when the link fails.

Communications links must have galvanic isolation between the interlocking equipment and any external circuits. Opto-isolators, or transformers are normally used to provide galvanic isolation. Some communications equipment provide galvanic isolation.

#### 2.5.2 High traffic areas

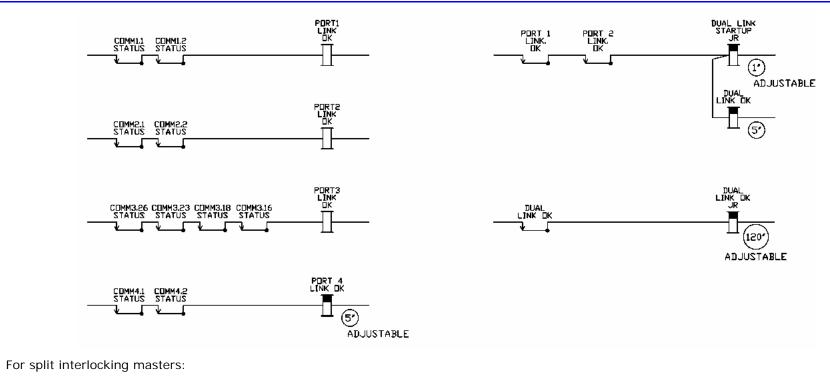

Two fully redundant communication links in constant use, with diverse paths are to be provided.

The communications equipment must use a secure no-break power supply. The communications links must not be disrupted for more than 15 seconds due to power supply disruptions.

Only point-to-point 9600 or 19200 bps, asynchronous, 8 data bit, 1 start bit, 1 stop bit, no parity, full duplex links should be used for main interlockings.

Multi-drop arrangements using Fibre Optic Modems for in-section signalling locations are acceptable, with a point to point link back to the Control System.

# 2.5.3 General traffic areas

Two communication links are to be provided, a primary and a secondary. The secondary link does not need to be in constant use. If the secondary link is not normally in use then it must be brought into operation automatically, with less than a 90 second disruption to operations. The secondary link must be mostly via diverse path to the primary link. The secondary link must automatically re-establish if it fails whilst in service.

Non-continuous secondary links must automatically disconnect after more than 90 seconds of correct operation of the primary link.

The communications equipment must use a secure power supply. The communications links must not be disrupted for more than 30 seconds due to power supply disruptions.

Point to point 9600 or 19200 bps asynchronous, 8 data bit, 1 start bit, 1 stop bit, no parity, full duplex links are preferred but Multi-drop 9600bps links may be used when point-to-point links are impractical.

## 2.5.4 Low traffic areas

A single communication link is required with an MTBF of greater than 2 years. A secondary link is desirable. The operation of the secondary link does not need to be automated.

The communications equipment should use a secure power supply. The communications links must not be disrupted for more than 60 seconds due to power supply disruptions.

Point to point 19200, 9600 or 1200bps asynchronous, 8 data bit, 1 start bit, 1 stop bit, no parity, full duplex links are preferred but Multi-drop 9600bps or 1200bps links may be used when point-to-point links are impractical.

# 2.6. Safety system communication link configuration

#### 2.6.1 General

Safety communication links must not have any buffering or "store and forward" provided in the communications equipment between the Microlok II equipment as per the requirements set out in the Microlok II Platform Safety Application Guidelines.

Typically "dark fibre" or a copper pair is provided and the approved Fibre Optic Modem arrangements, or analogue modems are provided as part of the signalling installation.

Communications links must have galvanic isolation between the interlocking equipment and any external circuits. Opto-isolators, or transformers are normally used to provide galvanic isolation. Some communications equipment provides galvanic isolation.

Particular configuration details are set out in the section on Serial links.

#### 2.6.2 High traffic areas

No single equipment, or cable failure shall cause an operational impact on the railway.

Fibre Optic communications links must be used.

Duplicated point to point links do not require a diverse link but they must have some physical diversity in the links.

Multi-drop links for slaves in more than 5 separate locations must have a loop arrangement with a redundant link. Typically Diversity Link Controllers (DLCs) would be used in this case, otherwise Fibre Optic Modem (FOMs) units would be used.

No more than 10 slave addresses are to be used on one link. This results in a poll cycle time of about 900mS for the link at about 90ms per slave at 19200bps using Fibre Optic Modems.

#### 2.6.3 General traffic areas

Single equipment, or cable failure can cause an operational impact on the railway.

Facilities must be provided so that the Signalling maintenance personnel can correct the failure without other assistance.

Fibre Optic communications links must be used.

Duplicated point to point links do not require a diverse link but they must have some physical diversity in the links.

Multi-drop links for slaves in more than 9 separate locations must have a loop arrangement with a redundant link. Typically Diversity Link Controllers (DLCs) would be used in this case, otherwise Fibre Optic Modem (FOMs) units would be used.

No more than 12 slave addresses are to be used on one link. This results in a poll cycle time of about 1080mS for the link at about 90ms per slave at 19200bps using Fibre Optic Modems.

## 2.6.4 Low traffic areas

No redundancy for availability is required.

Single equipment, or cable failure may cause an operational impact on the railway.

Fibre Optic communications links should be used for complete new installations. Modem links using copper cables are acceptable when new cable routes are not being provided.

The poll cycle time must be less than 2 seconds.

# 2.7. Equipment housing and cable route configuration

# 2.7.1 General

Equipment housings and cable routes must comply with specification alterations identified in the Proposal for Standard Specification alterations to address issues with 415V signalling power distribution, Surge protection installation guideline, and the Ancillary Equipment Temperature rating Installation guideline.

Passive temperature control is required on all locations, using a method of shade structures or "double skinning" and adequate ventilation.

Siting of any location must consider:

- Protection of the location from damage.

- 1 in 100 year flooding.

- Fire risk.

- Surge damage risk.

- Damage due to High voltage power faults.

Location layout must provide:

- Segregation for wiring and equipment for surge protection.

- Layout of equipment and wiring for minimise coupling of electrical noise onto sensitive circuits.

- Layout of equipment for ease of maintenance.

- Layout of equipment for temperature effects.

#### 2.7.2 High traffic areas

A well as complying with the ARTC Signalling Engineering standards requirements for protecting against fire damage and stopping the spread of fire, the limiting of fire damage should be considered in the design.

Passive fire protection should be provided so that cable routes can withstand an external fire without irreparable damage as per SPS 02 Environmental Conditions.

Routing of cable routes is to consider surge protection issues and proximity to High Voltage Earths for Earth Potential Rise (EPR) issues.

Duplicate cables or diverse cables must be physically separated or have appropriate physical protection so that it is improbable that both cables are damaged in the one incident.

Cables that can introduce significant surges must not be placed in close proximity to other cables prior to having passed through some surge protection.

A re-enterable cable route is required.

#### 2.7.3 General traffic areas

Passive fire protection should be provided so that cable routes can withstand an external fire without irreparable damage as per SPS 02 Environmental Conditions.

# 2.7.4 Low traffic areas

There are no additional requirements for Low traffic areas.

# 2.8. Microlok specific configuration issues

#### 2.8.1 General

Microlok application data must not use Look-up tables without a specific design guideline being approved for the particular use.

Microlok application data must not use Numeric blocks for purposes other than for configuration control without a specific design guideline being approved for the particular use.

External signalling circuits driven by Microlok Outputs must not have "stick" paths without a design review to confirm that short duration "false" outputs do not cause a hazard.

The LOGIC\_TIMEOUT default setting of 2 seconds must be used unless there is a specific problem. It may be set to no more than 4 seconds to address the problem. If this is not satisfactory then other solutions must be found.

The DELAY\_RESET default setting is 100mS. It should not normally be changed. It may be set at any value in the provided range to address a particular problem.

The RESET, QUICK.RESET system bits are not to be set by the application logic. The KILL system bit should be used instead.

The SELECTIVE.SHUTDOWN bits for the boards are not to be set by the application logic.

Timers less than 24 seconds can be delayed by more than 10% of their value. Consideration must be given to the impact of delays when using timers of less than 24 seconds. This may cause problems with timers used for speed control.

All direct vital output circuits must be powered via a contact of the VCOR or a repeat of the VCOR.

Safety critical faults detected by the application logic must set the KILL system bit. This shall include the CONFIGURE.ERROR bit.

Vital serial links are to be disabled by the loss of the CPS.STATUS system bit.

It is not necessary to fail a coded track circuit on loss of the CPS.STATUS system bit, however action is to be taken to ensure that track codes are not able to allow a potential safety hazard due to the event that caused the CPS.STATUS to become false.

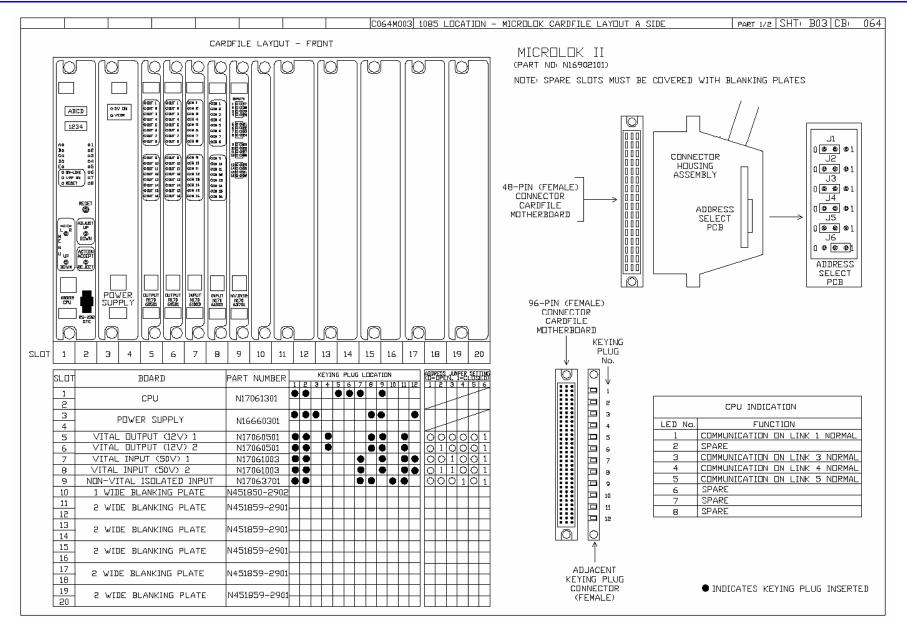

| Part<br>Number | Description                                      | Permitted<br>for High<br>Traffic use | Permitted<br>for General<br>Traffic use | Permitted<br>for Low<br>Traffic use | Notes |

|----------------|--------------------------------------------------|--------------------------------------|-----------------------------------------|-------------------------------------|-------|

| N17061301      | Central Processing<br>Unit                       | ~                                    | ✓                                       | $\checkmark$                        | 1     |

| N451232-1701   | Microlok 2 Executive<br>Software Revision<br>5.1 | √                                    | ✓                                       | ✓                                   | 2     |

| N16661203      | Power Supply                                     | ✓                                    | ✓                                       | $\checkmark$                        | 9     |

| N451910-7501   | CPS                                              | ✓                                    | ✓                                       | $\checkmark$                        |       |

| N17060101      | Vital Lamp Driver<br>Card                        | ×                                    | Limited Usage                           | $\checkmark$                        | 7     |

| N17060501      | Standard Vital<br>Output (12V)                   | $\checkmark$                         | ✓                                       | $\checkmark$                        | 3     |

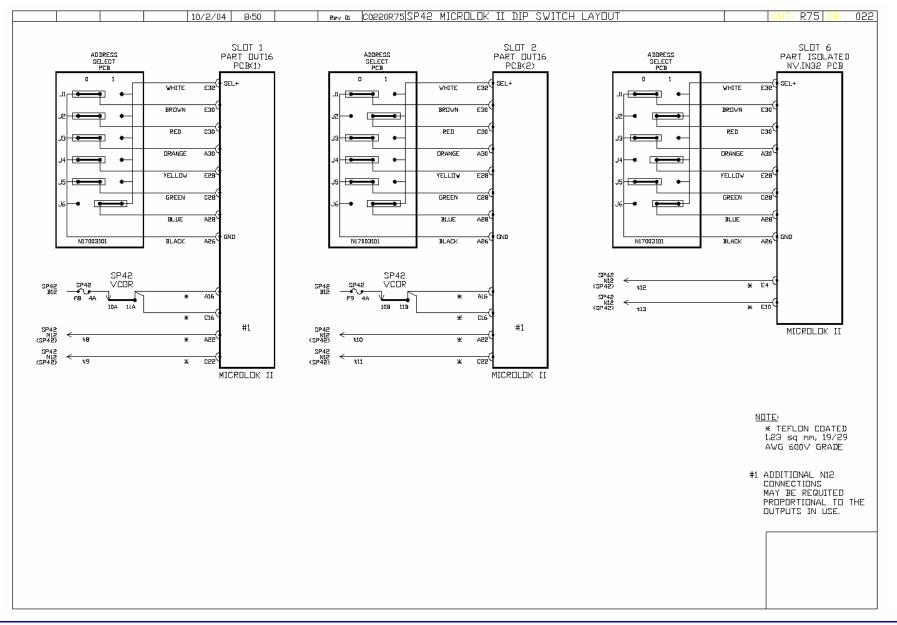

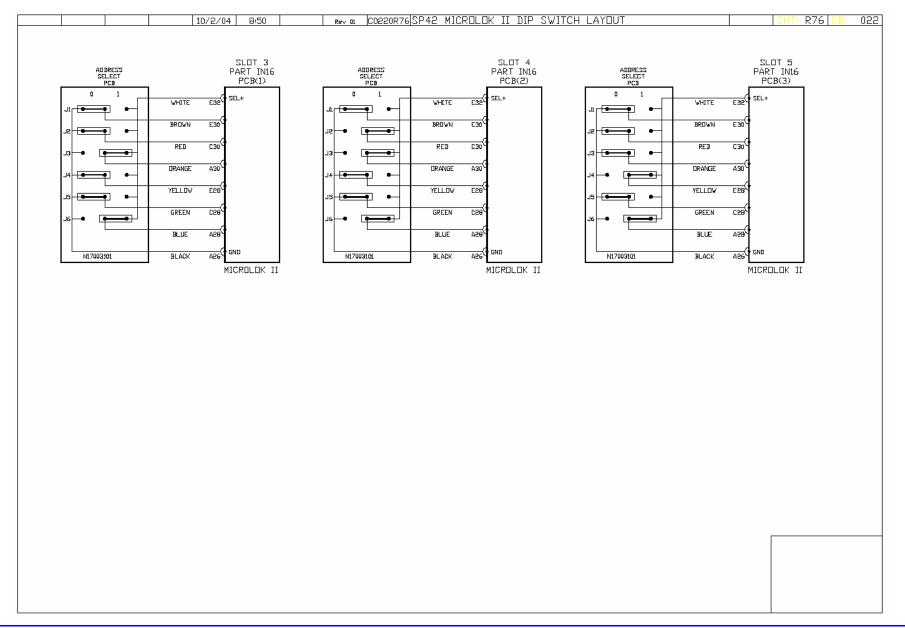

#### 2.8.2 Approved modules

| N17061001    | Vital Input (12V)                                  | ×             | Limited Usage | $\checkmark$                   | 4 |

|--------------|----------------------------------------------------|---------------|---------------|--------------------------------|---|

| N17061003    | Vital Input (50V)                                  | $\checkmark$  | ✓             | $\checkmark$                   | 4 |

| N17061501    | Non Vital Non<br>Isolated Input and<br>Output Card | Limited usage | Limited usage | ✓                              | 5 |

| N17061601    | Standard 8 Vital<br>Output, 8 Vital Input<br>(12)  | ×             | ×             | Permitted but<br>not preferred |   |

| N17062701    | Non Vital Isolated<br>Output Card                  | ~             | ~             | $\checkmark$                   |   |

| N17063701    | Non Vital Isolated<br>Input Card                   | ~             | ~             | ✓                              |   |

| N451910-0701 | Coded Track Circuit<br>PCBs                        | ×             | ~             | ✓                              | 8 |

| N17001102    | Isolation Module<br>(50V)                          | $\checkmark$  | ~             | ✓                              | 6 |

#### Notes

- 1. One spare serial port is to be wired out to interface terminals or a suitable connector.

- 2. Rev 3.2, Rev 3.4, and Rev 4.01 are approved for continued use but are not to be used on new installations. Alterations should upgrade to Rev 5.1.

- 3. Spare outputs shall preferably be left unwired. Where future stages will require additional outputs, spare outputs may be wired to interface terminals, and such outputs must be terminated with 220R 1W resistors. All outputs that are wired are to be wired via a disconnect terminal to permit disconnection as per the "Disconnection of Signalling Apparatus" Signalling Maintenance Procedure.

- 4. Spare inputs may be wired to interface terminals if required for future stages.

- 5. Only to be used for internal circuits. Care is required in allocating the N12 connections. The input circuits should use A13, C3, C13, C12 as the N12 connections. The output circuits should use A17, A21, A25, A29 as the N12 connections.

- 6. The isolation module should be provided with 15V power to ensure the output voltage is adequate.

- 7. Spare outputs may to be wired to interface terminals. All lamps outputs are to meet the requirements for disconnection as per the Microlok Computer Based Interlocking Signalling Maintenance Procedure SMP 38. If the usage is limited then use of the card is permitted based on failure impact meeting the design goals.

- 8. If permitted, the module is for use in non-electrified areas only. The application data is to contain 75% of the actual track length or a value set by the Engineer certifying the track as the default.

- 9. This is the Enhanced Power Supply card, launched by US&S as a direct replacement for the old N16660301. The Enhanced card has higher current capacities compared to the old card: 5VDC @ 5A (up from 3A), -12VDC @ 2A (up from 1A), +12VDC @ 1A (unchanged). At time of writing, the Power Calculation in the Microlok Tools software has not been updated, and designers should be aware that this may eliminate the need for external power supplies in some projects.

#### 2.8.3 Timers in High traffic areas

Timers set for less than 24 seconds must be reviewed to determine that they will not cause an operational impact or safety hazard if they are delayed by more than 10%.

### 2.8.4 Timers in General traffic areas

Based on the lower expected rail traffic conditions Timers set for less than 12 seconds must be reviewed to determine that they will not cause an operational impact or safety hazard if they are delayed by more than 10%.

### 2.8.5 Timers in Low traffic areas

Based on the lower expected rail traffic conditions Timers set for less than 6 seconds must be reviewed to determine that they will not cause an operational impact or safety hazard if they are delayed by more than 10%.

# 2.9. Microlok Platform Safety Application Guidelines

Personnel working with Microlok II should be familiar with the *Microlok II Programmable Controller, Platform Safety Application Issues.*

The issues identified in the Microlok II Platform Safety Application issues have been considered and addressed as follows:

| Issue                                 | Treatment                                                                                                                                                                     |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2                                  | Signal Design Quality Procedure QSDP16, and QSDP31 to verify the application image                                                                                            |

| 3                                     | Addressed by <i>Microlok Computer Based Interlocking</i> Signalling Maintenance<br>Procedure SMP 38                                                                           |

| 4, 5                                  | Addressed by this document.                                                                                                                                                   |

| 6                                     | Design, Review, and Verification on each design.                                                                                                                              |

| 7, 8                                  | ARTC Signalling Engineering Standards.                                                                                                                                        |

| 9                                     | ARTC Signalling Engineering Standards, and advice from US&S that the Microlok Executive software checks the Boolean logic trigger list as part of the start-up safety checks. |

| 10                                    | Addressed by this document.                                                                                                                                                   |

| 11                                    | ARTC Signalling Engineering Standards.                                                                                                                                        |

| 12                                    | Design, Review, and Verification on each design.                                                                                                                              |

| 13, 14                                | Addressed by this document.                                                                                                                                                   |

| 15                                    | Design, Review, and Verification on each design.                                                                                                                              |

| 16                                    | Addressed by this document.                                                                                                                                                   |

| 17                                    | Addressed by <i>Microlok Computer Based Interlocking</i> Signalling Maintenance<br>Procedure SMP 38.                                                                          |

| 18                                    | Signal Design Quality Procedure QSDP33                                                                                                                                        |

| 19                                    | Design, Review, and Verification on each design.                                                                                                                              |

| 20, 21, 22, 23                        | Addressed by this document.                                                                                                                                                   |

| 24                                    | Design, Review, and Verification on each design.                                                                                                                              |

| 25                                    | Addressed by this document.                                                                                                                                                   |

| 26                                    | Signalling Maintenance Procedure for MircoTrax.                                                                                                                               |

| 27                                    | Design, Review, and Verification on each design.                                                                                                                              |

| 28, 29, 30, 31, 32, 33,<br>34, 35, 36 | Addressed by this document.                                                                                                                                                   |

| 37, 38, 39                            | ARTC Signalling Engineering Standards.                                                                                                                                        |

| 40                                    | Addressed by <i>Microlok Computer Based Interlocking</i> Signalling Maintenance<br>Procedure SMP 38                                                                           |

| 41, 42                                | ARTC Signalling Engineering Standards.                                                                                                                                        |

| 43, 44, 45                            | Addressed by this document.                                                                                                                                                   |

| 46                                    | Addressed by <i>Microlok Computer Based Interlocking</i> Signalling Maintenance<br>Procedure SMP 38.                                                                          |

| 47                            | ARTC Signalling Engineering Standards.                                             |

|-------------------------------|------------------------------------------------------------------------------------|

| 48, 49, 50, 51                | Addressed by this document.                                                        |

| 52, 53, 54, 55, 56            | Design, Review, and Verification on each design.                                   |

| 57, 58, 59                    | Addressed by this document.                                                        |

| 60, 61                        | ARTC Signalling Engineering Standards.                                             |

| 62                            | Signal Design Quality Procedure QSDP16, and QSDP31 to verify the application image |

| 63, 64, 65, 66, 67, 68,<br>69 | Design, Review, and Verification on each design.                                   |

| 70                            | Addressed by this document.                                                        |

# 2.10. Track side equipment configuration

#### 2.10.1 Signals

#### 2.10.1.1. Direct control by Microlok II

#### <u>Aldridge</u>

Not currently approved for direct drive by Microlok II Vital Lamp Driver card.

#### <u>United</u>

The Mark 2 Outdoor 212mm, DC signal light requires a 24R, 25W WH25 series resistor fitted in the signal head when operated using a regulated 16.2V lamp supply.

- Up to 110m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 340m cable distance using 4mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

The Mark 2 Outdoor 212mm, DC signal light requires a 15R, 25W WH25 series resistor fitted in the signal head when operated using an un-regulated 13.6V battery supply.

- Up to 20m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

- Up to 60m cable distance using 4mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

The Mark 2 Outdoor 127mm, DC signal light requires a 12R, 25W WH25 series resistor fitted in the signal head when operated using a regulated 16.2V lamp supply.

- Up to 110m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 340m cable distance using 4mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

The Mark 2 Outdoor 127mm, DC signal light requires a 10R, 25W WH25 series resistor fitted in the signal head when operated using an un-regulated 13.6V battery supply.

- Up to 40m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

- Up to 110m cable distance using 4mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

The DC LED stencil indicator requires a 10R, 50W WH50 series resistor fitted in the signal head.

- Up to 110m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 340m cable distance using 4mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 20m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

- Up to 60m cable distance using 4mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

#### <u>Westinghouse</u>

The RM4 series outdoor, 212mm signal light requires a 15R, 25W WH25 series resistor fitted in the signal head.

- Up to 160m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 450m cable distance using 4mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 55m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

- Up to 160m cable distance using 4mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

The TR3 501 series tunnel or outdoor 127mm signal light requires a 10R, 25W WH25 series resistor fitted in the signal head.

- Up to 160m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 450m cable distance using 4mm<sup>2</sup> of twisted pair cable using regulated 16.2V lamp voltage.

- Up to 40m cable distance using 1.5mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

- Up to 110m cable distance using 4mm<sup>2</sup> of twisted pair cable using 13.6V battery supply as the lamp voltage.

#### 2.10.1.2. Relay control

Relay control of LED signals must be as per the LED signals controlled by relay circuits Design Guideline.

#### 2.10.2 Track Circuits

Track circuit limits are as per the ARTC Signalling Engineering Standards.

#### 2.10.3 Microtrax Coded Track Circuits

The cable from the location to the Microtrax Coded track, track interface unit must be less than 50m of 1.5mm<sup>2</sup> twisted pair cable, or 150m of 4mm<sup>2</sup> twisted pair cable unless a technical review is performed which determines an acceptable feed length for the particular Coded track circuit.

Microtrax Coded track circuits shunting sensitivity is affected by the loop resistance of the cable from the location to the trackside interface unit. The importance of the loop resistance increases as the length of the track increases.

The track interface panel must have RSA disconnect links on the connections to the rails to allow for disconnection as per *Microlok Computer Based Interlocking* Signalling Maintenance Procedure SMP 38 and *Microtrax* Signalling Maintenance Procedure SMP 37.

A OR22 resistor in the track interface unit is typically fitted in the trackside of the Track Interface unit to decrease the shunting sensitivity to at least 0.25 ohms.

A 0.25 ohm test shunt is used in certifying the Microtrax Coded Tracks.

#### 2.10.4 Relay noise suppression

Relays generate electrical noise when they are de-energised. This electrical noise can interfere with electronic or computerised equipment like the Microlok II.

Relays that are controlled by a circuit that is not exclusively within the location housing the relay are snubbed with a Contact suppressor (RC snubber 0.1uF plus 100R) fitted across the coil. These units are suitable for 12VDC, 24VDC, 50VDC relays. They may be used for 120VAC relays but this will operate the RC snubber at close to its 0.5W power rating. They are available from RS Components as stock number 210-364 for free wiring, and 210-370 with a fixing tab that can be secured under the bottom screw of a Q relay base.

Relays that are controlled by a circuit that is exclusively within the location housing the relay are snubbed with a 1N4007 diode fitted in the reverse direction across the coil. This method is suitable for 12VDC, 24VDC, and 50VDC relays only and it may not be suitable for polarised circuits. Fitting the diode across the relay coil means that the relay cannot be AC immune.

The recommendation in Microlok II manual SM-6400B to use Transorbs is not preferred, as these units have been found to be un-reliable.

In some cases a resistor can also be used for snubbing purposes, this will normally be for an AC circuit.

Relays directly driven by Microlok II must be snubbed.

All relays at a location with Microlok II are to be snubbed or the Microlok II segregated from the source of the electrical noise. The preferred method of segregation is by the use of twisted pair wiring, AC Immunising modules on the inputs, and Microlok II Isolation modules or relays on the outputs and physical separation.

### 2.10.5 Microlok II input circuits external to the location

Microlok II inputs that are wired external to the equipment location require immunity from sources of 50Hz AC, Traction currents, and general electrical noise as well as surges due to lightning.

Circuits that are wholly within a tunnel and do not travel within 100m of the tunnel portal do not require the surge protection.

The surge protection arrangement must consider 50Hz Earth Potential Rise (EPR) faults if both ends of the circuit are not at the same location.

Two methods are currently accepted for provision of immunity from any source of interference for circuits external to the location.

#### Method 1

Use Dekoron twisted pair cable and twisted pair wiring with double cut circuits, ensuring that the twisted pair is maintained throughout the whole circuit, and provide a 3 mode surge arrestor (line to line, and line to earth) at any external entry or exit to the equipment location.

Given:

- That the cumulative length of cable route that is within 3m of traction return rails or traction supply wire is less than 100m.

- Power cables that provide power to a load that is more than 10KVA and run parallel to the cable for more than 100m are separated by at least 300mm from the cable.

- Non-twisted cable and wiring does not exceed 3m circuit lentgh.

If the given conditions are not met then the circuit must be treated as per Method 2.

A surge arrestor based on a 290V three terminal ceramic arrestor is considered suitable. The holdover voltage for the arrestor must be greater than 75 volts.

Acceptable external circuit lengths for the 50V input card is 4,000m double cut Method 1 circuit length or 8,000m of wire length.

Acceptable external circuit lengths for the 12V input card is 400m double cut Method 1 circuit length or 800m of wire length.

#### Method 2 (Only permitted for 50V circuits)

Use traditional signalling cable or wire and Elsafe Immunisation module (216640) near to the Microlok II input.

Twisted pair wiring using the Dekoron cable as per Method 1 may be used.

Note that there cannot be two Elsafe immunisation modules (216640) in series in a circuit for dual Microlok II inputs as there would be a series voltage drop of about 30V across the Elsafe immunisation modules. In this case an Elsafe Gas arrestor (290V) module (216680) is provided at the feed point of the circuit.

The Elsafe immunisation module (216640) provides about 25dB attenuation at 50Hz.

Acceptable external circuit lengths for the 50V input card is 3,000m double cut Method 2 circuit length or 6,000m of wire length.

# 2.11. Cables and wiring

#### 2.11.1 Colour coding

Generally black wire is used for permanent control wiring. The Power supply wiring colour code is red for positive DC, Black for Negative DC, and Blue for un-earthed AC.

Paired cables or wires for control wirings will normally have black and white as a pair. The white is to be used for the negative or neutral side of the circuit, and black as the Positive or Active side of the circuit.

Some paired cables or wires for control wirings have red and black pairs. The black is used for the negative or neutral side of the circuit, and the red as the positive or active side of the circuit.

#### 2.11.2 General multi-core cable

CBI interface applications may use Olex Dekoron Instrumentation cable with an overall screen for signalling inputs and outputs. The cable must have a nylon jacket and a sacrificial PVC sheath added to the standard cable.

The standard Dekoron cables are twisted pair cables and need to be used as pairs to provide immunity to electrical noise and interference. These cables are permitted for use at voltages up to 130VAC or 150VDC/. Circuit currents should not normally exceed 6 amps, which is half the Manufacture's rated current.

The Dekoron based cable has 1.5mm<sup>2</sup> (7/0.50mm) conductors with an overall screen, in 4 pair, 8 pair, 12 pair, or 24 pair.

#### Stock Code Cable

001881069 TWISTED 1.5 mm<sup>2</sup>, 4 PAIR 001881010 TWISTED 1.5 mm<sup>2</sup>, 8 PAIR 001881028 TWISTED 1.5 mm<sup>2</sup>, 12 PAIR 001881036 TWISTED 1.5 mm<sup>2</sup>, 24 PAIR

#### 2.11.3 Internal Wire

Safety critical wiring in Location cases and Relay Rooms where a Computer Based Interlocking system is being used must use Mil-W-22759-16-16 wire due to problems with the thickness of insulation and the possibility of leaking plasticiser from the standard internal wire as specified in ARTC Engineering Standard SPS 45 *Cables for Railway Signalling Applications - Single Conductor Cables for Indoor Use.*

The wire is available from Cambridge Technologies as part number 16-ACFZ-1929. This is based on the US Military Standard Mil-W-22759-16-16-000.

System Configuration

The wire is also available as black and white twisted pair. Part Mil-W-22759-16-16-0+9 twisted at greater than 15 twists per metre.

This wire is insulated using extruded ETFE, which has good properties for physical abuse during installation, and in service.

The wire is 19/29 AWG,  $1.23 \text{mm}^2$  at 15.8 ohms/km. It is rated for 600 volts and  $150^{\circ}$ C. This wire may be used for safety critical circuits up to and including 120VAC. It is suitable for terminations in general terminals, the 48 way connectors for the Microlok II cardfile, and Q relay crimps.

For 48 way connectors, use twisted pair black & white cable 19/29 AWG, 1.23 mm<sup>2</sup> wires. Use Harting Part No. 09-06-000-8482 crimps for the 1.23mm<sup>2</sup> wire.

The Microlok II CPU 48 way connectors will need connections for serial links. Typically 24 AWG Cat 5 cable is used. Use Harting Part No. 09-06-000-8481 crimps for the 24 AWG Cat 5 cable.

The 96 way connector for the Microlok II non-vital card has insufficient space to use the  $1.23 \text{mm}^2$  wire so 19/34 AWG,  $0.4 \text{mm}^2$  wire is to be used for the 96 way connector output card, part number MiI-W-22759-16-22-000.

For 96 way connectors, use black 19/34 AWG, 0.4  $mm^2$  wire. Use Harting Part No. 09-06-000-8484 crimps for the 0.4  $mm^2$  wire.

#### Stock Code Cable

001881044 TWISTED 1 PAIR (INDOOR CABLE FOR MICROLOK 1.23mm<sup>2</sup>)

#### 2.11.4 Heavy duty cable

Heavy duty cable based on Dekoron cable can be used for lamp drive circuits, and coded track circuits.

#### Stock Code Cable

001887553 TWISTED 4 mm<sup>2</sup> 1 PAIR 001887561 TWISTED 4 mm<sup>2</sup> 8 PAIR

#### 2.11.5 Power cable for extended voltage Mains

ARTC Stock Code 1901883

CABLE POWER ELECTRICAL, 16mm<sup>2</sup>; 2 CORE; 7/1.7MM; PLAIN ANNEALED COPPER; RED, BLACK PVC/BLACK PVC/NYLON/ORANGE PVC SHEATH; 1000M DRUM;

ARTC Stock Code 1901891

CABLE, POWER, ELECTRICAL, 50mm<sup>2</sup>; 2 CORE 19/1.78MM PLAIN ANNEALED COPPER; RED, BLACK PVC/BLACK PVC/NYLON/ORANGE PVC SHEATH; 1000M DRUM;

#### 2.11.6 Fibre Optics

#### 2.11.6.1. General

Multi-mode fibre optic installations are preferred as they are more tolerant to poor environment conditions.

Single-mode fibre optic installations are to have a separate approval for each installation.

#### 2.11.6.2. Cable

Fibre Optic installation must be in accordance to AS-3080:2000 for Fibre Optics.

The multi-mode optical fibre cables shall have a graded-index of 62.5/125 micrometer, with a loss of less than 3.5dB/Km at 850nm.

Fibre Optic cable is to be outdoors type suitable for direct burial, or ducts, and termite resistant.

100% Insertion Loss (light source and power meter) testing of all terminated fibres must be performed in both directions at 850nm for multimode cables.

OTDR tests shall be performed at wavelength used by the Fibre Optic Modems.

#### 2.11.6.3. Fibre Management Enclosure

Terminate Fibre Optic cables in rack mount termination enclosure with patch panel, suitable for a minimum of 16 fibres.

Normally ST or FC connectors are used.

#### 2.11.6.4. Patch Leads

Patch leads are normally Multimode, Duplex, ST to ST, or FC to ST for connection to Fibre Optic modems.

Fibre Optic modems in normal use have ST connectors.

#### 2.11.6.5. Fibre Optic Modems

Currently the only approved Fibre Optic Modem is the OSD136 from Optical Systems Design.

Both single mode and multi-mode versions have been approved.

It is current practice to power the OSD136 from 5VDC via the DB25 connector where practical to reduce the operating temperature of the Fibre Optic Modem.

#### 2.11.6.6. Distance for Multimode fibre

Designs should limit the segments between OSD136 Multimode modems to a maximum of 5 Km of fibre optic cable after allowing for losses in connectors etc.

#### 2.11.6.7. Distance for single mode fibre

Designs should limit the segments between OSD136 single modems to a maximum of 40 Km of fibre optic cable after allowing for losses in connectors etc.

# 3. Serial Link Communications

# 3.1. Vital Serial Links

#### 3.1.1 General

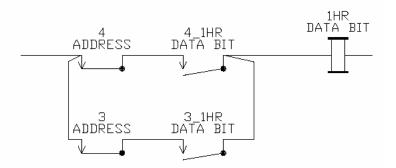

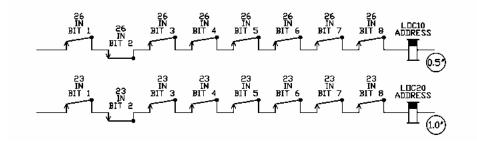

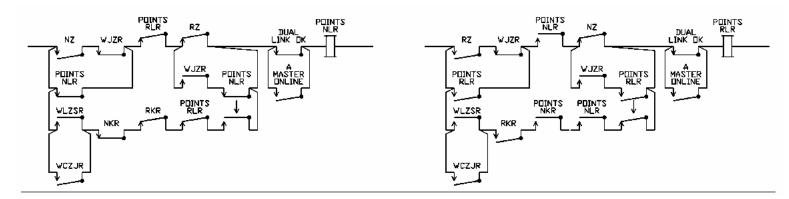

All Microlok II vital serial links at: each individual site, and within each section of the cable route, must have a unique serial link address unless they must have identical data because they are individual links of a duplicated link arrangement.

If a Microlok II vital serial link is to operate over cabling or communications multiplexing equipment that extends beyond the trackside signalling cables then an additional 8 bit address must be embedded into the vital serial link data. The application logic must check the additional address and not accept any data unless the address matches the normal address and the additional address.

The Microlok II serial ports have different priorities, port 1 having the highest priority, and port 4 having the lowest priority. Normally the priority of the serial ports will not impact on the design, however if all links are in use, and the CPU is expected to be heavily loaded, it is preferred to allocate the vital links as the lower port numbers.

# 3.1.2 Fibre Optic Links

These settings are for configurations using Fibre Optic Modems.

### 3.1.2.1. Master settings

| LINK:                      | COMMx           |

|----------------------------|-----------------|

| ADJUSTABLE ENABLE:         | 1               |

| PROTOCOL:                  | MICROLOK.MASTER |

| FIXED PORT:                | x;              |

| ADJUSTABLE BAUD:           | 19200;          |

| ADJUSTABLE KEY.ON.DELAY:   | 30;             |

| KEY.OFF.DELAY:             | 12;             |

| STALE.DATA.TIMEOUT:        | 4:SEC;          |

| POINT.POINT:               | 1;              |

| ADJUSTABLE MASTER.TIMEOUT: | 100:MSEC;       |

|                            |                 |

| ADDRESS:                   | XX              |

| ADJUSTABLE ENABLE:         | 1               |

STALE.DATA.TIMEOUT default is 4 seconds. It may be decreased or increased to a maximum of 6 seconds to address particular application issues.

POLLING.INTERVAL is normally left at the default and should only be adjusted in response to a particular problem. It should not be set above 200mS.

#### 3.1.2.2. Slave settings

| LINK:                    | COMMx          |

|--------------------------|----------------|

| ADJUSTABLE ENABLE:       | 1              |

| PROTOCOL:                | MICROLOK.SLAVE |

| FIXED PORT:              | x;             |

| ADJUSTABLE BAUD:         | 19200;         |

| ADJUSTABLE KEY.ON.DELAY: | 30;            |

| KEY.OFF.DELAY:           | 12;            |

| STALE.DATA.TIMEOUT:      | 4:SEC;         |

| POINT.POINT:             | 1;             |

| INTERBYTE.TIMEOUT:       | 0:MSEC;        |

| ADDRESS:                 | XX             |

| ADJUSTABLE ENABLE:       | 1              |

STALE.DATA.TIMEOUT should not be changed from the default of 4 seconds. It may be increased to a maximum of 6 seconds to address particular problems.

#### 3.1.3 Analogue Modems

Modems must have controlled carrier with a carrier startup time of less than 280 bit times. Typically at 9600 bps the carrier startup time is less than 30mS. Most modems are not suitable.

The Exicom 396 modem is approved for Microlok 2 vital serial links.

The Dataplex 210 short haul modem specifications are suitable, however the modem has not been tested at the time of writing.

#### 3.1.3.1. Master settings

| LINK:<br>ADJUSTABLE ENABLE:<br>PROTOCOL:          | COMMx<br>1<br>MICROLOK.MASTER |

|---------------------------------------------------|-------------------------------|

| FIXED PORT:<br>ADJUSTABLE BAUD:                   | 4;<br>9600;                   |

| ADJUSTABLE KEY.ON.DELAY:                          | 280;                          |

| ADJUSTABLE KEY.OFF.DELAY:                         | 20;                           |

| STALE.DATA.TIMEOUT:<br>ADJUSTABLE MASTER.TIMEOUT: | 4:SEC;<br>250:MSEC;           |

| POINT.POINT:                                      | 1;                            |

| ADDRESS:                                          | xx                            |

| ADJUSTABLE ENABLE:                                | 1                             |

MASTER.TIMEOUT should be set at 250mS and may be increased to 500mS to address particular problems.

STALE.DATA.TIMEOUT should not be changed from the default of 4 seconds. It may be increased to a maximum of 6 seconds to address particular problems.

POLLING.INTERVAL is normally left at the default and should only be adjusted in response to a particular problem. It should not be set above 200mS.

#### 3.1.3.2. Slave settings

| LINK:                          | COMMx          |

|--------------------------------|----------------|

| ADJUSTABLE ENABLE:             | 1              |

| PROTOCOL:                      | MICROLOK.SLAVE |

| FIXED PORT:                    | x;             |

| ADJUSTABLE BAUD:               | 9600;          |

| ADJUSTABLE KEY.ON.DELAY:       | 280;           |

| ADJUSTABLE KEY.OFF.DELAY:      | 20;            |

| ADJUSTABLE STALE.DATA.TIMEOUT: | 4:SEC;         |

| ADJUSTABLE POINT.POINT:        | 1;             |

| ADJUSTABLE POINT.POINT:        | l;             |

| ADDRESS:                       | xx             |

| ADJUSTABLE ENABLE:             | 1              |

POINT.POINT is set to 1 unless multi-drop analogue modems are used.

Baud is set to 9600 unless a particular modem's limitations require a lower speed.

#### 3.1.3.3. Exicom 396 modem settings

The modem needs to be configured for V.29 fast train, 9600bps, Half Duplex, Asynchronous, 10 bits/Character.

The modem can use 4 wire or 2 wire communication links. 4 wire communication links are preferred.

| Switch 1/1 ON Links S, and T Don't Care<br>Switch 1/2 ON Don't Care | Primary rate.                |

|---------------------------------------------------------------------|------------------------------|

| Switch 1 /3 ON                                                      |                              |

| Switch 1/4 ON                                                       | V.29 fast train              |

| Switch 1/5 OFF Don't Care                                           |                              |

| Switch 1/6 OFF                                                      | - 10dbm                      |

| Switch 1/7 OFF                                                      | -26dbm receive               |

| Switch 1/8 OFF Link L installed, Link K out.                        | Internal clock               |

| Switch 2/1 ON Link D installed, Link C out for                      | or 2 wire or Half duplex.    |

| Link C installed, D removed for 4 wire.                             |                              |

| Switch 2/2 OFF                                                      | Point to Point.              |

| Switch 2/3 OFF                                                      | No squelch                   |

| Switch 2/4 OFF                                                      | No RTS delay                 |

| Switch 2/5 OFF                                                      | No retrain                   |

| Switch 2/6 OFF                                                      | not used for this mode.      |

| Switch 2/7 OFF                                                      | not used for this mode.      |

| Switch 2/8 OFF                                                      | not used for this mode.      |

| Links N installed, M removed                                        | Pin 9 isolated               |

| Links R installed, P removed                                        | Pin 10 isolated              |

| Links A installed, B removed.                                       | 600 ohm receiver.            |

| Switch 3/1 OFF                                                      | Don't Care                   |

| Switch 3/2 OFF                                                      | Don't care                   |

| Switch 3/3 OFF                                                      | No link amplitude equalizer. |

| Switch 3/4 OFF                                                      | No receive delay equaliser   |

| Switch 3/5 OFF                                                      | No cable equalizer.          |

| Switch 3/6 OFF                                                      | No cable equalizer.          |

| Switch 3/7 OFF                                                      | No digital delay equalizer.  |

| Switch 3/8 ON                                                       | Ccts 140, & 141 disabled     |

|                                                                     |                              |

Links G installed, H removed. Links E installed, F removed. E-link removed

Signal ground isolated from protective ground.

Serial Link Communications

| Switch 4/1 OFF<br>Switch 4/2 OFF | 10 bits per character.                     |

|----------------------------------|--------------------------------------------|

| Switch 4/2 OFF                   | Async timing at Basic tolerance.           |

| Switch 4/4 ON                    | Asynchronous                               |

| 605 Plug terminals               | 4W TX 2, 3, and RX 4, 6.                   |

| 2W TX/RX 4,6                     | although document implies 2/3 is expected. |

#### Configuration

Design to provide a received signal levels to modems of at least 10dB above the minimum modems receive level.

Typically 5 km between modems is easily achieved.

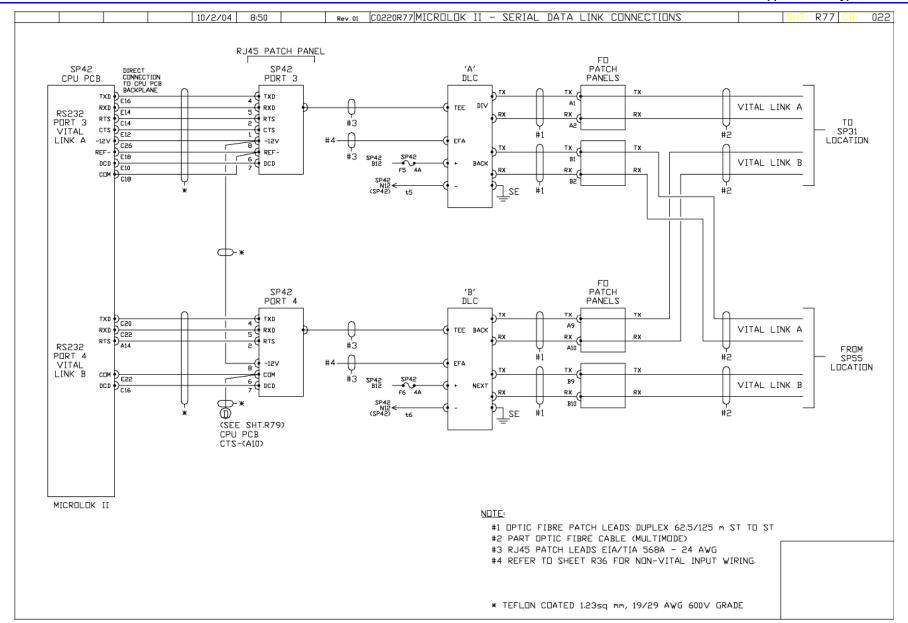

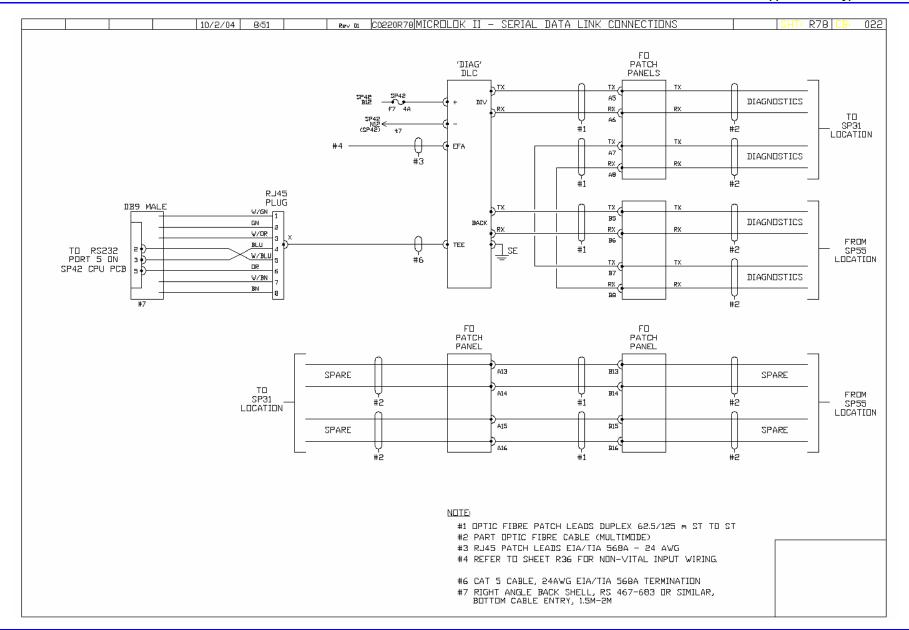

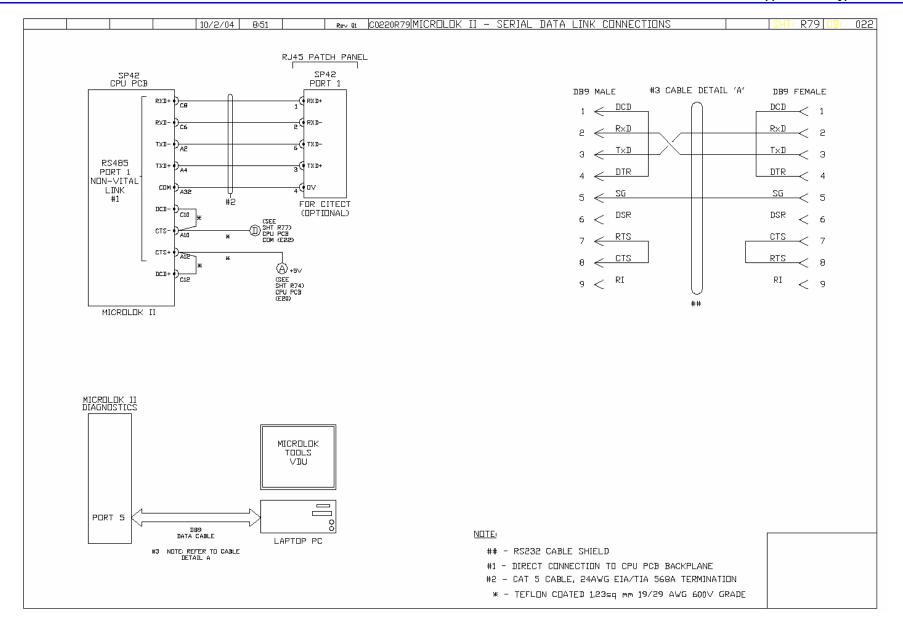

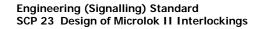

#### 3.1.4 Circuits

| RX:<br>TX: | Wire to Communications device or other Microlok port TX of the Microlok port.<br>Wire to Communications device or other Microlok port RX of the Microlok port. |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCD:       | Wire to Communications device or other Microlok port RTS of the Microlok port.                                                                                 |

| RTS:       | Wire to Communications device or other Microlok port DCD of the Microlok port.                                                                                 |

| CTS:       | Hold in the OFF state.                                                                                                                                         |

| Modem DTR: | Line should be held in the ON state for analogue modems, but may be left<br>unused for Fibre Optic Modem.                                                      |

### 3.1.5 Conversion between RS485 and RS232

The Alfatron A440 RS232-RS422 converter is approved for use on Microlok Vital Serial Links. The Alfatron A440 is used because it provides the RTS, and DCD control links as well as the TXD, and RXD.

The Alfatron A440 does not provide galvanic isolation. Careful consideration is required in the choice of power arrangements for the Alfatron A440 and other serial communications equipment to ensure the installation is not exposed to surges via the serial communications link.

#### 3.1.6 Wiring

Category 5 telecommunications cable using 24 AWG wire may be used for RS485 wiring within the location or building.

Category 5 telecommunications cable using 24 AWG wire may be used for RS232 wiring within the location or building to a maximum length of 5 metres.

RS232 wiring up to 15 metres is permitted using shielded cable designed for RS232 applications.

The twisted pair ETFE Teflon internal wire may be used for RS485 wiring for distances up to 5 metres.

# 3.2. Genisys links (Control system link)

Genisys requires an asynchronous communications link with 8 data bits, no parity, 1 start bit, and 1 stop bit with speed (in order of preference) of 19200 or 9600 bps. Where the communications line quality is low, 1200 bps may be used if a reliable connection cannot be established at 9600 bps.

Depending on the configuration the primary link is:

- Full duplex leased line modems at 19200, or 9600 bps or

- A full duplex Telstra DDS (Direct Data Service) operating at, 19200 or 9600 bps;

and the secondary link is:

- A full duplex, 19200, or 9600 bps leased line modems; or

- Dial-up modems set for full duplex, 9600 bps.

Serial Link Communications

External switching between primary and secondary links can be performed by Black box SW111AE RS232 Fallback switch.

#### 3.2.1 Slave

These settings are for Genisys slaves of either ATRICS or Phoenix Control System masters using point to point direct connections or Modems.

| COMMx         |

|---------------|

| 1             |

| GENISYS.SLAVE |

| x;            |

| 19200;        |

| 15:SEC;       |

| CONSTANT;     |

| 1;            |

|               |

| xxx           |

| 1             |

|               |

#### 3.2.2 Master

The Master Genisys arrangement would only be used where a Microlok is acting as the control system, for example, a push-button panel with a Microlok providing the non-vital interface between the panel and the interlocking. The settings shown are for the panel interface communicating with a single-sided interlocking master.

| LINK:<br>ADJUSTABLE ENABLE:<br>PROTOCOL: | COMMx<br>1<br>GENISYS.MASTER |

|------------------------------------------|------------------------------|

| FIXED PORT:                              | x;                           |

| ADJUSTABLE BAUD:                         | 19200;                       |

| ADJUSTABLE STALE.DATA.TIMEOUT:           | 15:SEC;                      |

| ADJUSTABLE CARRIER.MODE:                 | CONSTANT;                    |

| ADJUSTABLE MASTER.TIMEOUT:               | 300:MSEC;                    |

| ADJUSTABLE POINT.POINT:                  | 1;                           |

|                                          |                              |

| ADDRESS:                                 | xxx                          |

| ADJUSTABLE ENABLE:                       | 1                            |

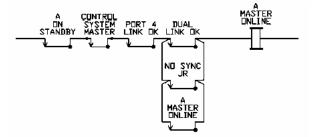

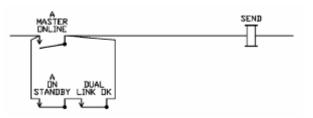

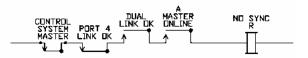

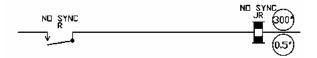

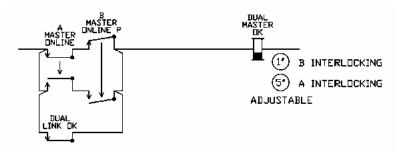

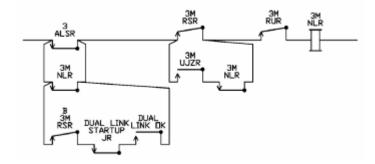

Where a dual hot standy interlocking is used, STALE.DATA.TIMEOUT must not be set to more than 2 seconds, in order for the hot standby changeover to work.

# 3.2.3 Circuits

| RX:<br>TX: | Wire to Communications device or other Microlok port TX.<br>Wire to Communications device or other Microlok port RX. |

|------------|----------------------------------------------------------------------------------------------------------------------|

| DCD:       | Wire to Communications device or hold in the ON state.                                                               |

| RTS:       | Normally leave disconnected unless using Multi-drop communications or Half-<br>duplex modems.                        |

| CTS:       | Hold in the OFF state                                                                                                |

| Modem DTR: | Should normally be held ON.                                                                                          |

| Modem RTS: | Should normally be held ON.                                                                                          |

# 3.2.4 Conversion between RS232 and RS485

The Adam 4520 RS232-RS485 converter is approved for use in Genisys Serial Links.

Version 1.4

The Adam 4520 provides galvanic isolation on the serial link. The preferred use is for the Adam 4520 to be powered from the Microlok II B12/N12 supply, and the RS485 side is connected to the Microlok II serial port.

The Adam 4520 is normally left in its default settings of 9600bps, 10 bit. The RTS line on the RS232 interface must be held ON.

#### 3.2.5 Wiring

Category 5 telecommunications cable using 24 AWG wire may be used for RS485 wiring within the location or building.

Category 5 telecommunications cable using 24 AWG wire may be used for RS232 wiring within the location or building to a maximum length of 5 metres.

RS232 wiring up to 15 metres is permitted using shielded cable designed for RS232 applications.

The twisted pair ETFE Teflon internal wire may be used for RS485 wiring for distances up to 5 metres.

### 3.2.6 Modem Configuration

The modem currently preferred by Engineering Standards and Services Signals for the non-vital link is the Westermo TD-35LV. When interfaced to ATRICS, Communications & Control Systems will specify different modems.

The TD-35 is designed for industrial use and incorporates several features to facilitate reliable operation, including:

- Low supply voltage can be powered directly from the battery-backed 12V Microlok supply, ensuring that the modem works even if the 120V supply is lost, and no step-up transformer is required;

- Full galvanic isolation of all ports, including the power supply connection;

- Watchdog function monitoring hardware, software, and power supply. In the event of internal fault, the watchdog will reset the modem enabling communications to be restored automatically;

The modem also provides DIP switches which can be used to set many of the operating parameters of the modem without requiring a computer to initialise the AT commands. Refer to the TD-35 manual for the location of the switch groups in the modem.

| Switch Group | Genisys Master end                                            | Genisys Slave end                 |  |

|--------------|---------------------------------------------------------------|-----------------------------------|--|

| SW1          | 1 – 2 ON (Leased line answering)                              | 1 off, 2 ON (Leased line calling) |  |

|              | 3 – 8 off                                                     |                                   |  |

| SW2          | 1 – 3 ON, 4 off (19200 baud)                                  |                                   |  |

|              | OR                                                            |                                   |  |

|              | 1 off, 2 – 3 ON, 4 off (9600 baud)                            |                                   |  |

|              | 5 – 6 ON, 7 off (8 data bits, No parity)                      |                                   |  |

|              | 8 off (1 Stop bit)                                            |                                   |  |

| SW3          | 1 – 2 off, 3 ON, 4 – 8 off (sets commonly used AT parameters) |                                   |  |

| SW4          | 1 – 4 ON (automatic line speed)                               |                                   |  |

|              | 5 – 6 off                                                     |                                   |  |

|              | 7 ON (4-wire mode for leased line)                            |                                   |  |

|              | 8 off                                                         |                                   |  |

3.2.6.1. Leased Line Settings

When using the modems on a leased line, all of the modem configuration can be achieved by use of the switches.

For leased line operation, 4-wire is preferred. Where problems are experienced, 2-wire mode may be used by setting SW4-7 off, and changing the telephone line connections appropriately. The telecommunications service provider should be contacted to arrange to have the problems investigated and corrected.

| Switch Group | Genisys Master end                                            | Genisys Slave end               |  |

|--------------|---------------------------------------------------------------|---------------------------------|--|

| SW1          | 1 – 2 off (P                                                  | 1 – 2 off (PSTN dial-up)        |  |

|              | 3 –                                                           | 3 – 8 off                       |  |

| SW2          | 1 – 3 ON, 4 off (19200 baud)                                  |                                 |  |

|              | OR                                                            |                                 |  |

|              | 1 off, 2 – 3 ON, 4 off (9600 baud)                            |                                 |  |

|              | 5 – 6 ON, 7 off (8 data bits, No parity)                      |                                 |  |

|              | 8 off (1 Stop bit)                                            |                                 |  |

| SW3          | 1 – 2 off, 3 ON, 4 – 8 off (sets commonly used AT parameters) |                                 |  |

| SW4          | 1 – 4 ON (autor                                               | 1 – 4 ON (automatic line speed) |  |

|              | 5 – 8 off                                                     |                                 |  |

3.2.6.2. Dial-up Settings

For dial-up operation, the interlocking end will normally be the dialling modem. A fallback switch will detect failure of the primary link, and trigger the modem to dial by asserting the DTR line to the modem. A computer must be used to configure the dialling settings for the modem using the command string AT&A1&B1&D3S0=0&Z0=n (where n is the phone number the modem is to dial). The modem at the control system end must be configured by computer with the command string AT&A1S0=2. Instructions should be provided in the circuit book and the maintenance instructions. Because the TD-35 has two connection options for the RS-232 port, the maintenance instruction must also include a warning to ensure the Microlok is disconnected from the modem before a computer is connected to the modem.

Modem AT commands used:

| &A1   | Ignore characters from the computer / Microlok during the call establishment phase |

|-------|------------------------------------------------------------------------------------|

| &B1   | Dial the stored number when DTR line rises                                         |

| &D3   | Perform soft reset when DTR line falls                                             |

| S0=x  | Auto-answer after x rings (zero disables auto answer)                              |

| &Z0=n | Store the phone number n in phone number memory 0                                  |

# 3.3. Control line states

#### 3.3.1 RS232 Control Lines

OFF state for control lines is -12V. ON state for control lines is +12V.

# 3.3.2 RS422/RS485 Control

OFF state for control lines is -ve terminal to 0V, +ve terminal to +5V.

ON state for control lines is -ve terminal to +5V, +ve terminal to 0V.

# 3.3.3 RS423 Control

OFF state for control lines is -6V.

ON state for control lines is +6V.

Note that the link setting for port 3 is normally set for RS232 so although port 3 is described as RS423 it is normally configured as a RS232 port.

# 4. Application Logic Design

# 4.1. Introduction

The Microlok II development system tools are to be used to develop and compile an application logic program, debug the program, and upload the application program to the Microlok II central processing unit (CPU) card.

For the comprehensive procedures to create the complete Microlok II application program, reference should be made to the US&S Microlok II System Application Logic Programming Guide. SM-6800D manual.

The application logic is to be designed in accordance with the Signal Design Quality Procedures QSDP16: Microlok File Control, Microlok Data Design and Factory Acceptance Testing, QSDP31: Retesting of Microlok Data, QSDP33: Checking of Microlok Circuits and Data Designs.

Design Engineers are to ensure the application logic is produced utilising the current approved Microlok II development tools and compilation software.

In general the application logic is based on or derived from the Signalling Circuit Design Standards. It is important to note all the features that can be programmed into the Microlok II system but are not or cannot be part of current relay design methodology, and the features that are part of current relay design methods which are not essential or necessary for the satisfactory operation of computer based interlockings and non-vital equipment.

Typical examples of these are:

- Replication of magnetically latched relays in principle.

- Removal of back contact proving for relay down proving purposes only.

- Removal or addition of relay features not relevant to 'software' relays.

- Specific maintenance indications and diagnostics.

- Timing and indication features that would be an expensive addition to conventional systems.

# 4.2. Design Process

The following steps should be followed when producing Microlok II application designs.

- The Design Engineer identifies the system configuration requirements such as the Microlok II circuit boards to be used, system interconnects, vital and non-vital I/O requirements, and all required interlocking logic.

- The application logic is created utilising a standard text editor to create the data file. It is recommended that NOTEPAD+ be used for this purpose. This file is given a filename extension of "ml2"

- The Microlok II logic compilation software is to be used to process the completed application logic data file. The compilation software produces an application source file (mlp extension) and a listing file (mll extension). The listing file contains a summary of the application program, as well as any errors detected in the source file.

- The application logic file may need to be corrected using the text editor and run through the compiler again.

- The compiled application source file may be uploaded to the appropriate Microlok II cardfile installation utilising the Microlok II Maintenance Tools program.

# 4.3. System Limitations

• There can be no more than 4095 assign statements in the Boolean Logic section. This includes the total number of ASSIGN and NV.ASSIGN statements and the timer bits. Where the number of assign statements exceeds 3000, or the number of defined bits exceeds 3500, the system may become heavily loaded. Designers will need to pay particular

Application Logic Design

attention during testing to ensure that the system will be stable, and alternative configurations may need to be considered.

- There is a combined limit on the number of timers, tables, and numeric blocks that may be defined, this limit is 399.

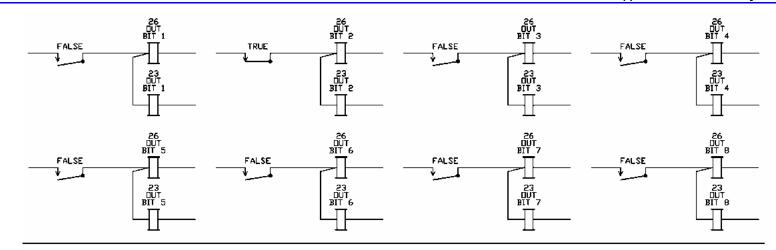

- A single ASSIGN or NV.ASSIGN statement may assign to no more than 32 bits.

- A bit used in the output list of an assign statement may trigger no more than 50 assignments, tables, blocks, or coded outputs.

- A maximum of 499 statements can be awaiting execution at any time on each of the execution queues for ASSIGN and NV.ASSIGN statements.

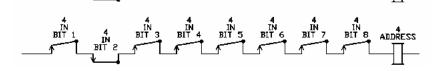

- A maximum of 128 data bit inputs and 128 data bit outputs, per address may be defined for transmission over a vital serial link. (Microlok Protocol)

- A maximum of 512 data bit inputs and 512 data bit outputs, per address may be defined for transmission over a non-vital serial link. (Genisys Protocol)

# 4.4. Standardisation of OCS Control of Interlockings

#### 4.4.1 Background

Entrance – exit style interlockings in NSW have developed over the years and have a number of features and constraints in the design.

Some of these have resulted from a system that was developed from using magnetically latched RLR relays for signal routes, and thermal approach locking release timers, which required an (N)R function, and circuits using direct button interfaces on the control panel.